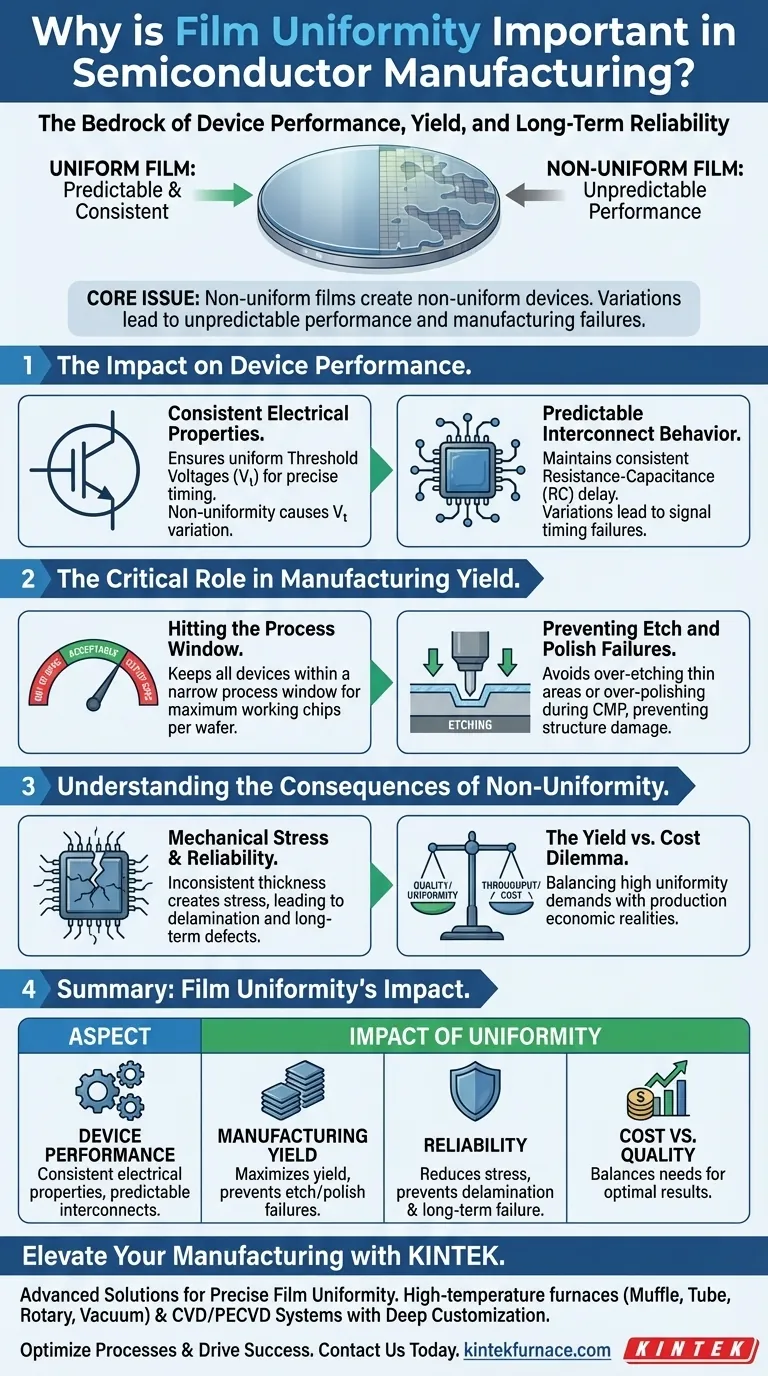

在半导体制造中,薄膜均匀性是器件性能、制造良率和长期可靠性的基石。 它是确保硅片上数十亿晶体管的每一个都可预测和一致地运行的关键因素。没有它,大规模生产功能性集成电路将是不可能的。

核心问题很简单:不均匀的薄膜会产生不均匀的器件。当薄膜厚度在晶圆上变化时,晶体管和互连线的电气和物理特性也会变化,从而导致性能不可预测和大规模的制造缺陷。

对器件性能的影响

在现代芯片的纳米尺度上,即使薄膜厚度出现微小变化,也会对最终器件的功能产生巨大影响。

一致的电气特性

沉积薄膜的厚度直接控制着基本的电气特性。例如,晶体管中的栅极氧化层控制着其开关行为。

不均匀的栅极氧化层意味着不同位置的晶体管将具有不同的阈值电压 (Vt),导致它们在不同时间开启。这种变异性破坏了复杂电路运行所需的精确时序。

可预测的互连行为

同样,金属和介电层的厚度决定了连接晶体管的导线的电阻-电容 (RC) 延迟。

这些薄膜的差异会导致信号在芯片上传输时间不一致。某些路径会变得太慢,从而导致时序故障,使整个芯片报废。

在制造良率中的关键作用

均匀性不仅仅关乎性能;它本身就是成功制造器件的先决条件。制造过程中的每一步都是以均匀的初始表面为假设进行校准的。

进入工艺窗口

半导体制造在极其狭窄的工艺窗口内运行,该窗口定义了给定步骤的可接受参数范围。

出色的薄膜均匀性确保了整个晶圆上的所有器件都落在这个关键窗口内。不均匀性会将器件推到“规格之外”,直接导致良率——即每晶圆的工作芯片百分比——下降。

防止刻蚀和抛光缺陷

后续的制造步骤,如刻蚀和化学机械抛光 (CMP),高度依赖于薄膜厚度。

如果薄膜不均匀,刻蚀过程可能会在较薄区域完全去除薄膜,而尚未完成对较厚区域的图案化。同样,CMP 可能会过度抛光较薄的区域,从而损坏下面的结构。

了解不均匀性的后果

追求均匀性是对抗物理和化学限制的持续斗争。未能加以管理会带来严重的后果。

机械应力和可靠性

当薄膜厚度不一致时,会在整个晶圆上产生机械应力梯度。

这些应力点可能导致一系列长期可靠性故障,包括薄膜分层(剥落)、开裂以及器件寿命期间出现的其他物理缺陷。

良率与成本的困境

实现近乎完美的均匀性在技术上要求很高且成本昂贵。能够实现更高均匀性的沉积设备通常吞吐量较低或成本较高。

工程师必须不断权衡收紧均匀性要求与生产的经济现实。这种完美质量与制造成本之间的权衡是该行业的核心挑战。

根据您的目标评估均匀性

您如何处理薄膜均匀性取决于您的具体角色和目标。

- 如果您的主要重点是器件设计: 您必须将预期的薄膜变化纳入您的模拟模型中,以确保您的芯片足够稳健,即使存在轻微的工艺缺陷也能正常工作。

- 如果您的主要重点是工艺集成: 您的目标是选择和优化沉积和刻蚀工艺,以最大限度地减少晶圆内变化,并为所有制造步骤最大限度地扩大工艺窗口。

- 如果您的主要重点是可靠性工程: 您必须分析薄膜不均匀性如何产生应力点,并利用这些数据来预测和减轻长期故障模式。

最终,控制薄膜均匀性等同于控制最终产品的性能、良率和可靠性。

摘要表:

| 方面 | 薄膜均匀性的影响 |

|---|---|

| 器件性能 | 确保一致的电气特性和可预测的互连行为 |

| 制造良率 | 使器件保持在工艺窗口内,并防止刻蚀/抛光缺陷 |

| 可靠性 | 减少机械应力,防止分层和长期故障 |

| 成本与质量 | 平衡均匀性需求与生产经济性,以获得最佳结果 |

借助 KINTEK 的先进解决方案提升您的半导体制造水平! 我们利用卓越的研发和内部制造能力,为各种实验室提供高温炉系统,如马弗炉、管式炉、旋转炉、真空和气氛炉,以及 CVD/PECVD 系统。我们强大的深度定制能力确保精确的薄膜均匀性,以满足您独特实验要求,从而提高器件性能、良率和可靠性。立即联系我们,探讨我们如何优化您的工艺并推动成功!

图解指南

相关产品

- 用于化学气相沉积设备的多加热区 CVD 管式炉设备

- 定制多功能 CVD 管式炉 化学气相沉积 CVD 设备机

- 射频 PECVD 系统 射频等离子体增强化学气相沉积技术

- 滑轨式 PECVD 管式炉(带液体汽化器 PECVD 机)

- 用于拉丝模纳米金刚石涂层的 HFCVD 机器系统设备