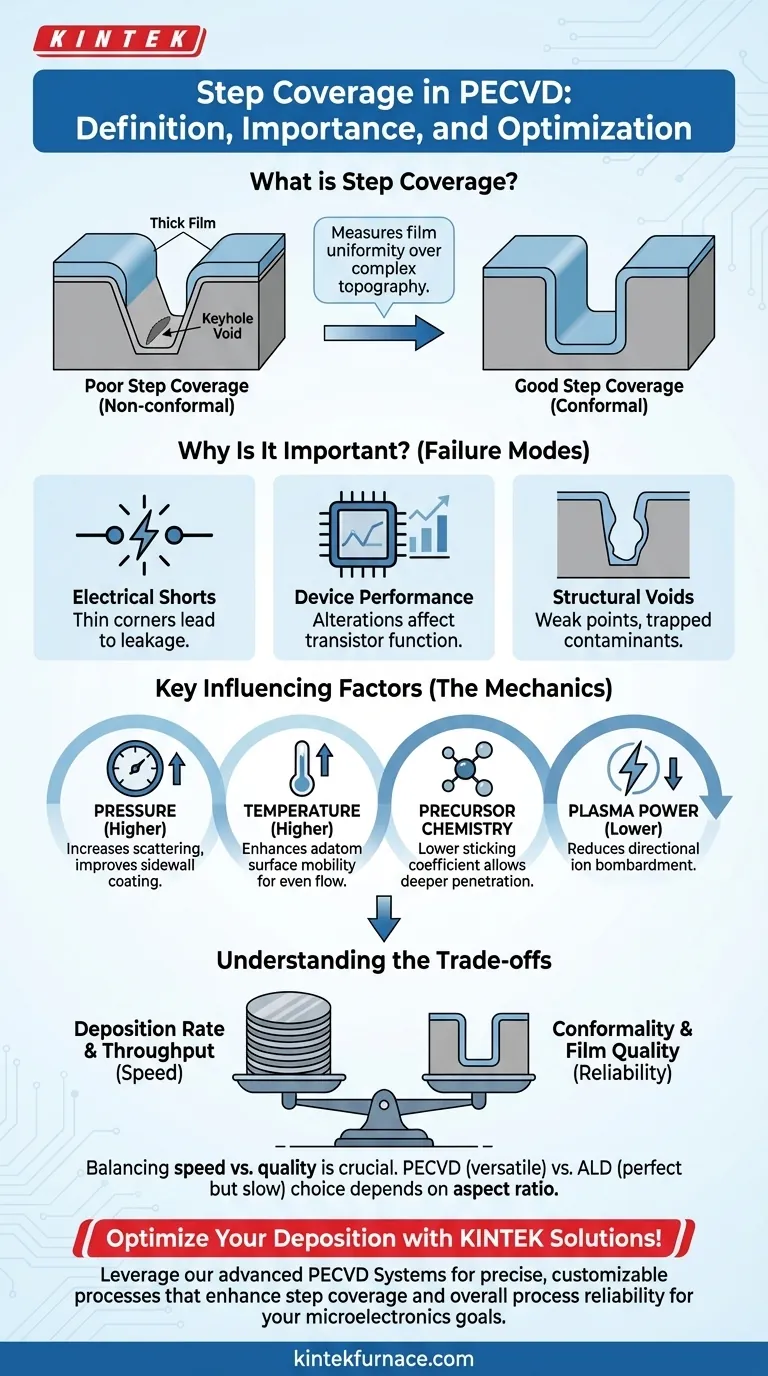

在薄膜沉积中,台阶覆盖率是一个关键指标,它定义了沉积的薄膜如何均匀地贴合基板的底层形貌。对于等离子体增强化学气相沉积(PECVD),它衡量薄膜在陡峭台阶、深沟槽和其他复杂三维特征上保持其厚度的能力。这种质量不仅仅是一个几何上的好奇心;它是现代微电子器件功能和可靠性的基本要求。

台阶覆盖率的核心挑战是克服几何“阴影效应”。可以将其想象成从一个方向喷漆复杂物体与将其浸入油漆桶中的区别。PECVD的目标是后者,确保每个角落都得到均匀的涂层,这对于防止微小电路中的电气故障和结构弱点至关重要。

PECVD中台阶覆盖率的机理

要理解为什么台阶覆盖率如此关键,我们必须首先研究它是如何实现的以及哪些因素影响它。这是沉积物种的方向性与其着陆后在表面上移动的能力之间的微妙平衡。

“好”与“差”的台阶覆盖率如何定义?

台阶覆盖率的质量通常由其保形性(conformality)来描述。完全保形薄膜具有100%的台阶覆盖率,意味着其厚度在特征的顶部、底部和侧壁上是相同的。

差的台阶覆盖率是非保形的。这通常导致薄膜在顶部表面很厚,在侧壁上变薄,在沟槽的底部角落最薄(或缺失)。在极端情况下,这可能导致空隙或“钥匙孔”,因为特征的顶部在底部完全填充之前就闭合了。

等离子体在辅助沉积中的作用

与纯热过程不同,PECVD利用等离子体在较低温度下产生反应性化学物质。这对台阶覆盖率有双重影响。

等离子体产生了更高浓度的反应性自由基,可以改善阴影区域的沉积。然而,它也产生了电场,可能导致离子加速撞击基板,从而导致更具方向性的、视线(line-of-sight)的沉积,这可能会加剧阴影效应。关键在于平衡这些相互竞争的机制。

关键影响因素

实现良好的台阶覆盖率需要精确控制多个工艺参数。

-

压力: 较高的工艺压力会增加气相碰撞,使薄膜前驱物的到达更加随机化和非定向化。这种散射效应显著改善了薄膜覆盖侧壁的能力。

-

温度: 提高基板温度可以增强沉积原子(adatoms)的表面迁移率。这使得它们在着陆后可以在表面上“流动”,从高浓度区域(如顶部角落)迁移到低浓度区域(如沟槽底部),从而使薄膜厚度趋于一致。

-

前驱体化学: 前驱体气体的选择至关重要。具有较长寿命和较低粘附系数(碰撞后粘附的概率)的分子更有可能在反应前在特征内部反弹,从而带来更好的保形性。

-

等离子体功率和频率: 降低射频(RF)功率可以减少离子轰击及其相关的方向性,从而改善覆盖率。等离子体的频率(低频与高频)也会改变离子能量分布,为工艺优化提供了另一个调节手段。

为什么差的台阶覆盖率是一个关键的失效模式

在半导体制造中,台阶覆盖率中看似微小的缺陷可能对整个器件造成灾难性的后果。

确保电气隔离

介电薄膜,如二氧化硅(SiO₂),用于隔离导电层。如果台阶覆盖率很差,薄膜在金属线的拐角处会变得危险地薄。这会产生薄弱点,可能导致电流泄漏或完全的电气短路,使电路无法使用。

维持器件性能

现代晶体管,如FinFET,具有复杂的三维结构。栅极介质必须完美均匀地包裹住晶体管的“鳍片”。这种关键层因台阶覆盖率不足而造成的任何减薄都会改变晶体管的电学特性,导致性能不可预测和器件过早失效。

防止结构空洞

随着非保形薄膜的堆积,沟槽的顶部角落比底部生长得更快。这可能导致沟槽顶部闭合,在薄膜内部封闭一个空洞或钥匙孔。这些空洞是结构弱点,可能会捕获污染物并损害器件的机械完整性。

理解权衡

为完美的台阶覆盖率进行优化并非没有代价。工程师必须将保形性与其他关键制造指标进行平衡。

沉积速率与保形性

有利于优异台阶覆盖率的工艺条件——例如高压力和低功率——通常会导致沉积速率较慢。在高产量制造中,这种权衡直接影响吞吐量和成本。必须找到一个平衡点,既能满足器件的最低可靠性要求,又能最大限度地提高生产速度。

薄膜质量与覆盖率

改变温度和等离子体条件以提高表面迁移率也会改变薄膜的固有特性,如其密度、化学成分和机械应力。仅为覆盖率而设计的激进工艺可能会产生应力过大的薄膜,导致之后出现开裂或分层。

PECVD与替代方法

虽然PECVD是一种多功能的“主力军”,但它也有局限性。对于先进逻辑和存储芯片中最苛刻、高深宽比的特征,通常需要其他方法。例如,原子层沉积(ALD)因其固有的特性,可提供近乎完美的100%台阶覆盖率,但其沉积速率明显低于PECVD。

根据目标做出正确的选择

您对台阶覆盖率的方法应由您应用的特定要求决定。

- 如果您的主要重点是快速涂覆简单、平面的表面: 您可以优先考虑高沉积速率,因为台阶覆盖率不是一个重要问题。

- 如果您的主要重点是中等深宽比(例如2:1)特征的绝缘: 经过良好优化的平衡压力、温度和速率的PECVD工艺将是您最有效的解决方案。

- 如果您的主要重点是高深宽比沟槽(例如>10:1)的完美保形性: 您必须优先考虑提高表面迁移率和降低方向性的条件,即使是以牺牲吞吐量为代价,并且可能需要评估ALD作为必要的替代方案。

掌握台阶覆盖率的原理是制造可靠、高性能微结构的基础。

总结表:

| 方面 | 描述 |

|---|---|

| 定义 | 薄膜厚度在基板形貌(如台阶和沟槽)上的均匀性。 |

| 重要性 | 在微电子学中防止电气短路,确保器件可靠性,并维持结构完整性。 |

| 关键因素 | 压力、温度、前驱体化学、等离子体功率和频率影响台阶覆盖率。 |

| 权衡 | 沉积速率、薄膜质量和保形性之间的平衡;在高深宽比特征中,PECVD与ALD的比较。 |

使用KINTEK的先进解决方案优化您的薄膜沉积! 我们利用卓越的研发和内部制造能力,为各种实验室提供高温炉系统,如马弗炉、管式炉、回转炉、真空与气氛炉以及CVD/PECVD系统。我们强大的深度定制能力确保与您独特实验需求的精确对齐,提高台阶覆盖率和整体工艺可靠性。立即联系我们,讨论我们如何支持您的微电子制造目标!

图解指南

相关产品

- 滑轨式 PECVD 管式炉(带液体汽化器 PECVD 机)

- 倾斜旋转等离子体增强化学气相沉积 PECVD 管式炉

- 用于化学气相沉积设备的多加热区 CVD 管式炉设备

- 定制多功能 CVD 管式炉 化学气相沉积 CVD 设备机

- 带真空站 CVD 设备的分室式 CVD 管式炉